数字电子技术 - 触发器

触发器是一种具有两个稳定状态的顺序数字电子电路,可用于存储一位二进制数据。触发器是所有存储设备的基本构建块。

触发器的类型

- S-R 触发器

- J-K 触发器

- D 触发器

- T 触发器

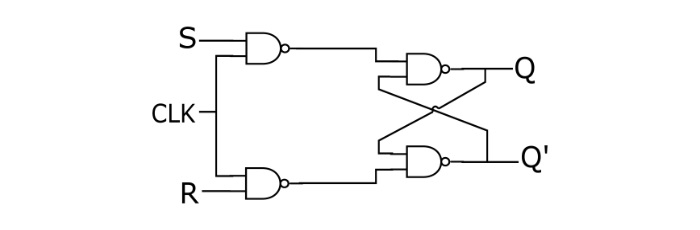

S-R 触发器

这是最简单的触发器电路。它有一个设置输入 (S) 和一个重置输入 (R)。当在此电路中将 S 设置为有效时,输出 Q 将为高电平,而 Q' 将为低电平。如果将 R 设置为有效,则输出 Q 为低电平,而 Q' 为高电平。一旦输出建立,电路的结果就会保持,直到 S 或 R 发生变化,或者电源关闭。

S-R 触发器真值表

| S | R | Q | 状态 |

|---|---|---|---|

| 0 | 0 | 0 | 否改变 |

| 0 | 1 | 0 | 重置 |

| 1 | 0 | 1 | 设置 |

| 1 | 1 | X |

S-R触发器特性表

| S | R | Q(t) | Q(t+1) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | X |

| 1 | 1 | 1 | X |

S-R 触发器的特性方程

$$\mathrm{Q(t \: + \: 1) \: = \: S \: + \: R' \: Q(t)}$$

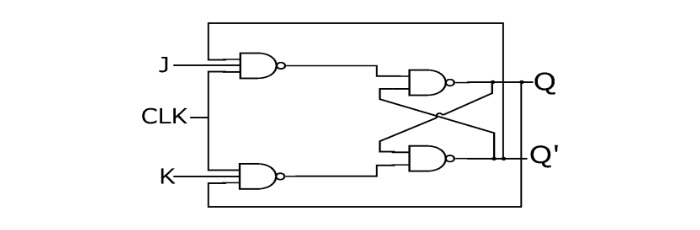

J-K 触发器

由于 SR 触发器中对应于 S=R=1 的状态无效,因此需要另一个触发器。JK 触发器仅在正或负时钟转换下运行。JK 触发器的操作类似于 SR 触发器。当输入 J 和 K 不同时,输出 Q 在下一个时钟沿取 J 的值。

当 J 和 K 都为低时,输出不会发生变化。如果 J 和 K 都为高,则在时钟边沿,输出将从一种状态切换到另一种状态。

JK 触发器的真值表

| J | K | Q | 状态 |

|---|---|---|---|

| 0 | 0 | 0 | 否更改 |

| 0 | 1 | 0 | 重置 |

| 1 | 0 | 1 | 设置 |

| 1 | 1 | 切换 | 切换 |

JK触发器特性表

| J | K | Q(t) | Q(t+1) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

JK触发器的特性方程

$$\mathrm{Q(t \: + \: 1) \: = \: j \: k \: Q(t)' \: + \: K'Q(t)}$$

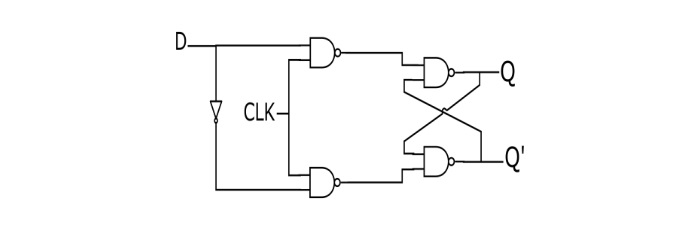

D触发器

在D触发器中,输出只能在正或负时钟转换时改变,而当输入在其他时间改变时,输出将保持不受影响。D触发器通常用于移位寄存器和计数器。D触发器输出状态的变化取决于时钟的有效转换。输出 (Q) 与输入相同,仅在时钟有效转换时发生变化

D 触发器真值表

| D | Q |

|---|---|

| 0 | 0 |

| 1 | 1 |

D 触发器的特性方程

$$\mathrm{Q(t \: + \: 1) \: = \: D}$$

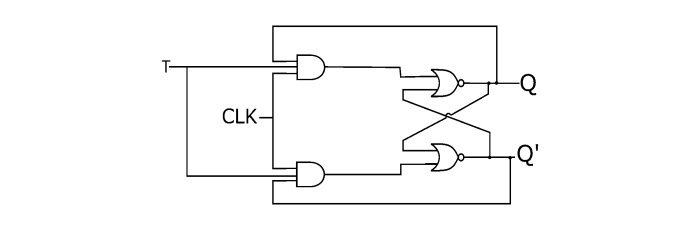

T 触发器

T 触发器(切换触发器)是 JK 触发器的简化版本。T 触发器是通过将 J 和 K 输入连接在一起而获得的。触发器有一个输入端和时钟输入。这些触发器被称为 T 触发器,因为它们能够切换输入状态。切换触发器主要用于计数器。

T 触发器的真值表

| T | Q(t) | Q(t+1) |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

T 触发器的特性方程

$$\mathrm{Q(t \: + \: 1) \: = \: T'Q(t) \: + \: TQ(t)' \: = \: T \: \oplus \: Q(t)}$$

触发器的应用

- 计数器

- 移位寄存器

- 存储寄存器等