数字电子技术 - 锁存器

锁存器是一种异步时序电路,其输出会随着所施加输入的变化而立即变化。锁存器用于在数字系统中存储 1 位信息,因此它被视为最基本的存储元件。

在本章中,我们将详细解释数字电子技术中的锁存器及其类型和应用。

什么是锁存器?

在数字电子技术中,锁存器是一种可以存储 1 位信息的异步时序电路。它用作数字电路中的基本存储元件。

锁存器可以有两个稳定状态,即设置和重置。置位状态用逻辑 1 表示,复位状态用逻辑 0 表示。由于这两个稳定状态,锁存器也称为双稳态多谐振荡器。锁存器的状态根据施加的输入切换。

关于锁存器,最重要的一点是它们没有用于同步的时钟信号。这就是为什么它们被称为异步时序电路。

逻辑门是锁存器的基本组成部分。由于没有使用同步和时钟信号。因此,锁存器在输入信号施加后立即运行。

锁存器的特性

下面解释了锁存器的一些关键特性 −

- 锁存器可以存储 1 位数字信息,可以使用逻辑 0 或逻辑 1 表示。因此,锁存器主要用作数字电路中的存储元件。

- 锁存器具有反馈机制,允许它们保持当前状态,直到下一个输入被应用。

- 锁存器的操作完全由施加的输入控制,这意味着锁存器的输出根据输入信号的变化进行更新。

锁存器的类型

以下是数字电路和系统中使用的主要锁存器类型 −

- SR 锁存器

- JK闩锁

- D 闩锁

- T 闩锁

现在让我们详细讨论每种类型的闩锁。

SR 闩锁

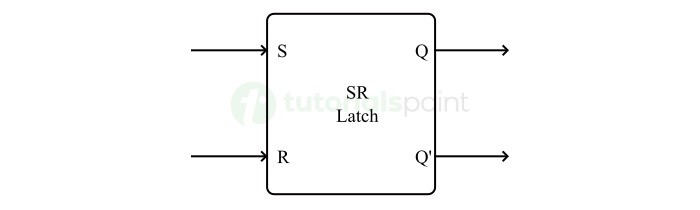

SR 闩锁是一种具有两条输入线的闩锁,指定为 S 和 R。其中,S 表示设置输入,R 表示重置输入。因此,它也被称为设置-重置闩锁。

SR 闩锁具有两个稳定状态,即设置状态 (S) 和重置状态 (R)。 SR 锁存器的框图如下图所示。

对于 SR 锁存器,S 输入将输出 Q 设置为 1,将 Q' 设置为 0。另一方面,R 输入将输出 Q 设置为 0,将 Q' 设置为 1。如果 S 和 R 输入都为高,则锁存器处于禁用状态。

以下真值表 − 描述了不同输入组合的 SR 锁存器的完整操作

| 输入 | 输出 | 注释 | ||

|---|---|---|---|---|

| S | R | Q | Q' | |

| 0 | 0 | Q | Q' | 无变化 |

| 0 | 1 | 0 | 1 | 重置状态 |

| 1 | 0 | 1 | 0 | 设置状态 |

| 1 | 1 | X | X | 禁止状态 |

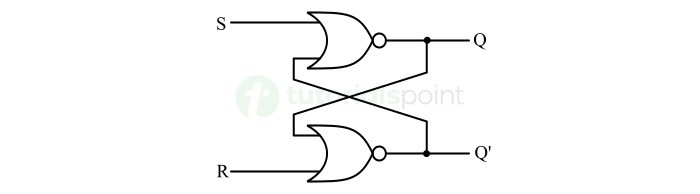

SR 锁存器可以通过以交叉耦合的方式连接两个 NOR 门来实现,如下图所示。

JK 锁存器

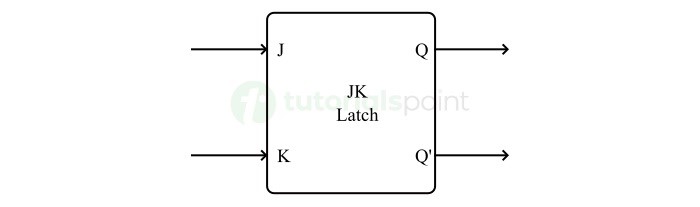

JK 锁存器是另一种类型的锁存器,它有两个输入,即 J 和 K。这里,输入 J 类似于 SR 锁存器中的 S 输入,输入 K 类似于 R 输入。

JK 锁存器的操作类似于 SR 锁存器的操作,但它没有禁止状态。相反,它具有切换状态,当输入 J 和 K 都为 1 时,输出 Q 和 Q' 会交换其状态。

因此,JK 锁存器主要是为了克服 SR 锁存器中的禁用状态问题而设计的。

JK 锁存器的框图如下图所示 −

下面给出的真值表描述了 JK 锁存器在不同输入组合下的操作 −

| 输入 | 输出 | 注释 | ||

|---|---|---|---|---|

| J | K | Q | Q' | |

| 0 | 0 | Q | Q' | 无变化 |

| 0 | 1 | 0 | 1 | 重置状态 |

| 1 | 0 | 1 | 0 | 设置状态 |

| 1 | 1 | Q' | Q | 切换状态 |

从该真值表中可以清楚地看出,通过实现切换状态可以解决禁用状态的问题。

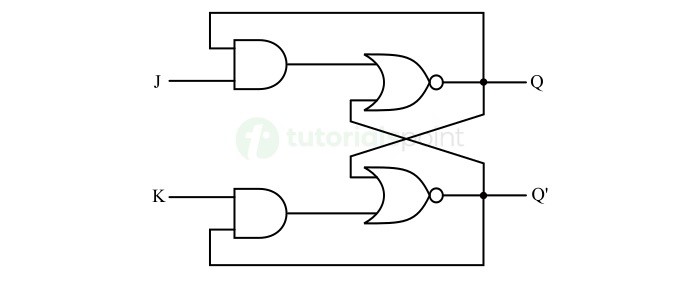

JK 锁存器的逻辑电路由两个 NOR 门和两个 AND 门组合而成,如下图所示。

D 锁存器

D 锁存器,也称为数据锁存器或透明锁存器,是一种双稳态多谐振荡器,具有两个输入信号,即 D(数据)输入和 E(启用)输入。

只要 E 输入为高电平,D 锁存器的输出 Q 就与 D 输入线上施加的输入相同。当 E 输入变为低电平时,D 锁存器的输出保持原样,直到新输入应用于 D 输入。

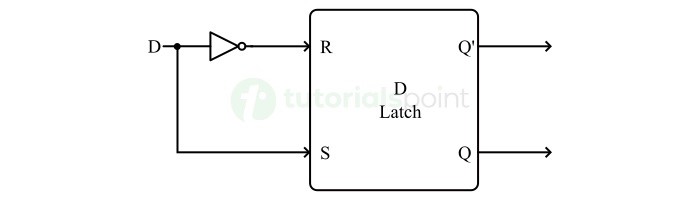

下图显示了 D 锁存器的框图。

下面给出的真值表解释了 D 锁存器的操作 −

| 输入 | 输出 | 注释 | ||

|---|---|---|---|---|

| D | E | Q | Q' | |

| 0 | 0 | Q | Q' | 无变化 |

| 0 | 1 | 0 | 1 | 重置状态 |

| 1 | 0 | Q | Q' | 无变化 |

| 1 | 1 | 0 | 设置状态 | |

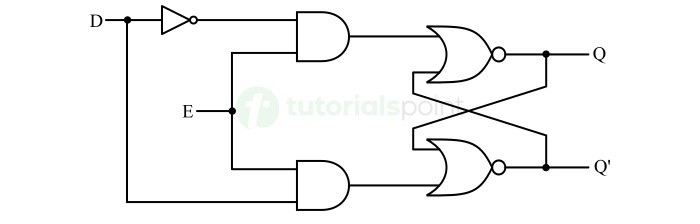

D 锁存器的逻辑电路图如下图所示 −

T 锁存器

T 锁存器是一种当逻辑 1 施加到其输入线时切换其输出状态 (Q) 的锁存器。因此,它也被称为切换锁存器。

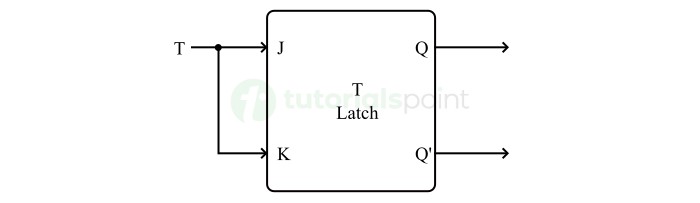

T 锁存器是通过将 JK 锁存器的 J 和 K 输入连接在一起来实现的,如下面的框图所示。

描述 T 锁存器操作的真值表如下所示 −

| 输入 | 当前状态 | 下一个状态 | ||

|---|---|---|---|---|

| T | Q | Q' | Q | Q' |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

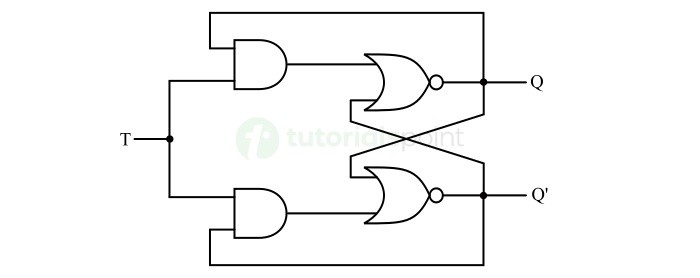

T 锁存器的逻辑电路图如下图所示 −

锁存器的应用

锁存器在数字电子领域有多种应用。它们是数字系统中用于存储一位信息的最基本的存储组件。

这里列出了一些锁存器的常见应用 −

- 锁存器在数字系统中用作 1 位存储元件。

- 锁存器用于设计数字寄存器,用于在微处理器和微控制器中存储和处理数据。

- 锁存器用于设计触发器,触发器基本上是同步锁存器。

- 锁存器还用于通信系统中的临时数据存储或缓冲目的。

结论

在本章中,我们解释了数字系统中使用的不同类型的锁存器以及锁存器的一些应用示例。

总之,锁存器是由逻辑门组成的 1 位存储设备。它是一种异步顺序逻辑电路,没有用于同步的时钟信号。

在数字系统中,锁存器用于实现一些关键功能,如临时数据存储、数据流控制等。